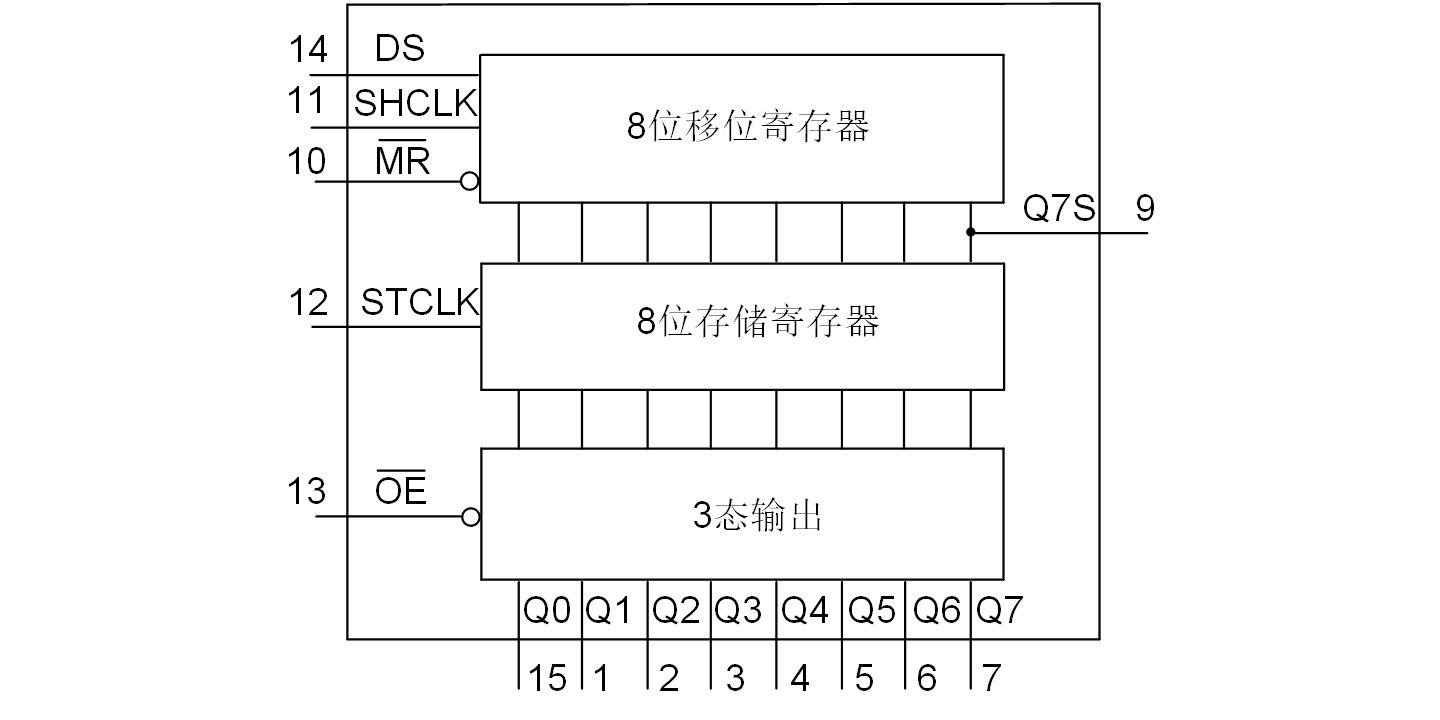

SLP74HC595包含了8位串行输入、并行输出的移位寄存器,为D型存储寄存器提供数据。该存储寄存器具有并行三态输出。

移位寄存器和存储寄存器具有相互独立的时钟。在移位寄存器输入时钟(SHCLK)上升沿,数据被移出。在存储寄存器输入时钟(STCLK)上升沿,各寄存器数据传输到存储寄存器中。如果两个时钟上升沿同时到来,移位寄存器始终领先存储寄存器一个时钟脉冲。

移位寄存器具有串行输入(DS)以及串行标准输出(Q7S),用于级联。同时所有8个移位寄存器都带有异步复位(低电平有效)。存储寄存器设有8位三态总线驱动输出。输出使能输入端(OE)为低电平时,存储寄存器的值就输出。输出使能输入端(OE)为高电平时,除Q7S之外所有输出端均处于高阻抗状态。

工作电压范围:2V~6.0V

8位串行输入并行输出移位

具有三态输出的存储寄存器

CMOS电平输入

ESD保护性能:

HBM>2000V

CDM>1000V

闩锁性能超过100mA

额定温度范围:-40°C~+85°C和-40°C~+125°C

| 产品名称 | 封装形式 | 打印名称 | 环保等级 | 包装 | 备注 |

|---|---|---|---|---|---|

| SLP74HC595SC | SOP-16-225-1.27 | 74HC595 | 无卤 | 料管 | |

| SLP74HC595SCTR | SOP-16-225-1.27 | 74HC595 | 无卤 | 编带 | |

| SLP74HC595JSTR | TSSOP-16-225-0.65 | 74HC595 | 无卤 | 编带 |

| 标题 | 类型 | 大小 (KB) | 日期 | 下载最新中文版本 |

|---|---|---|---|---|

| SLP74HC595 | 301 | 2024-03-25 | SLP74HC595 简要版说明书 |